Ahh thanks that makes much more sense. I am still starting to explore PMCs so sorry for my beginner questions.

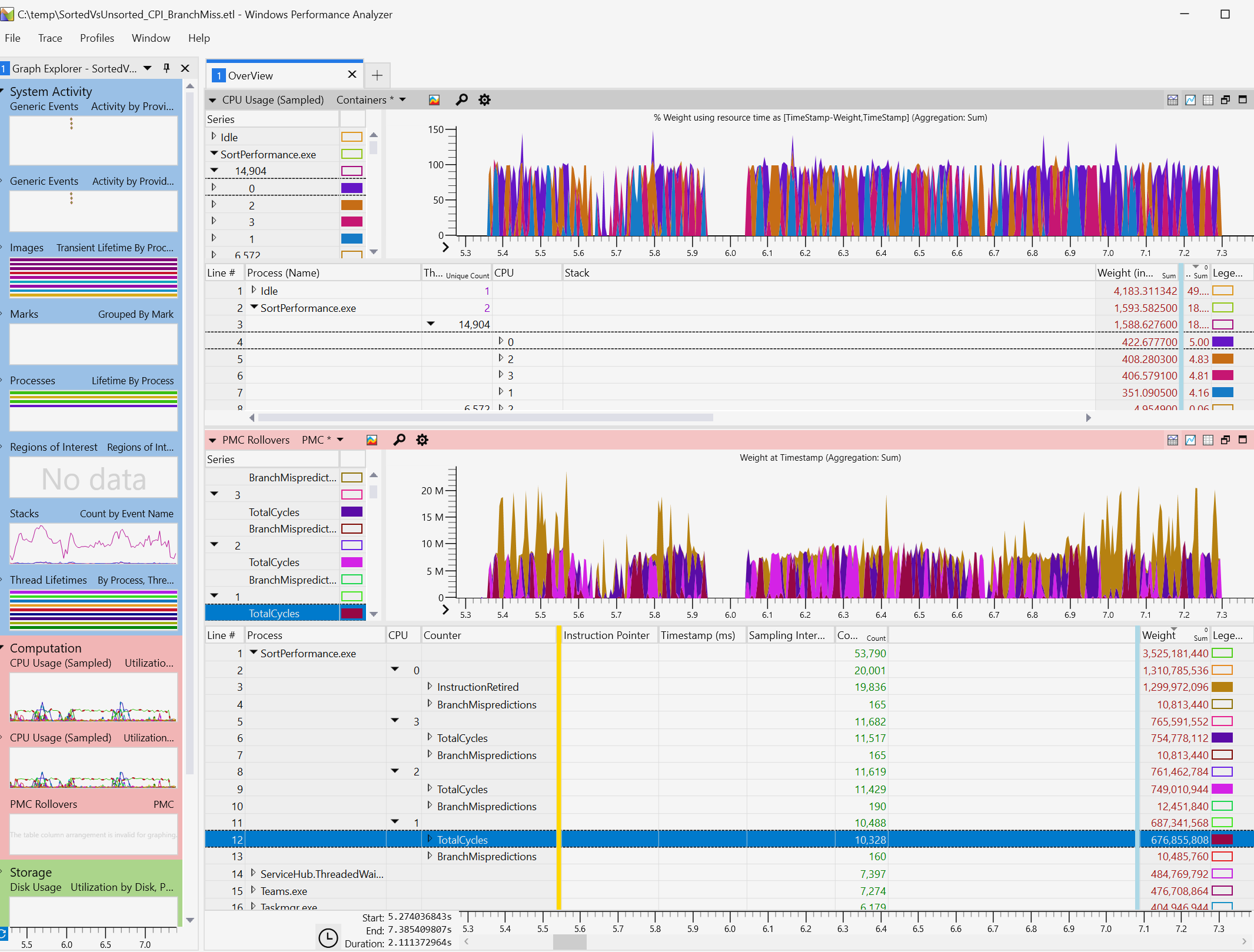

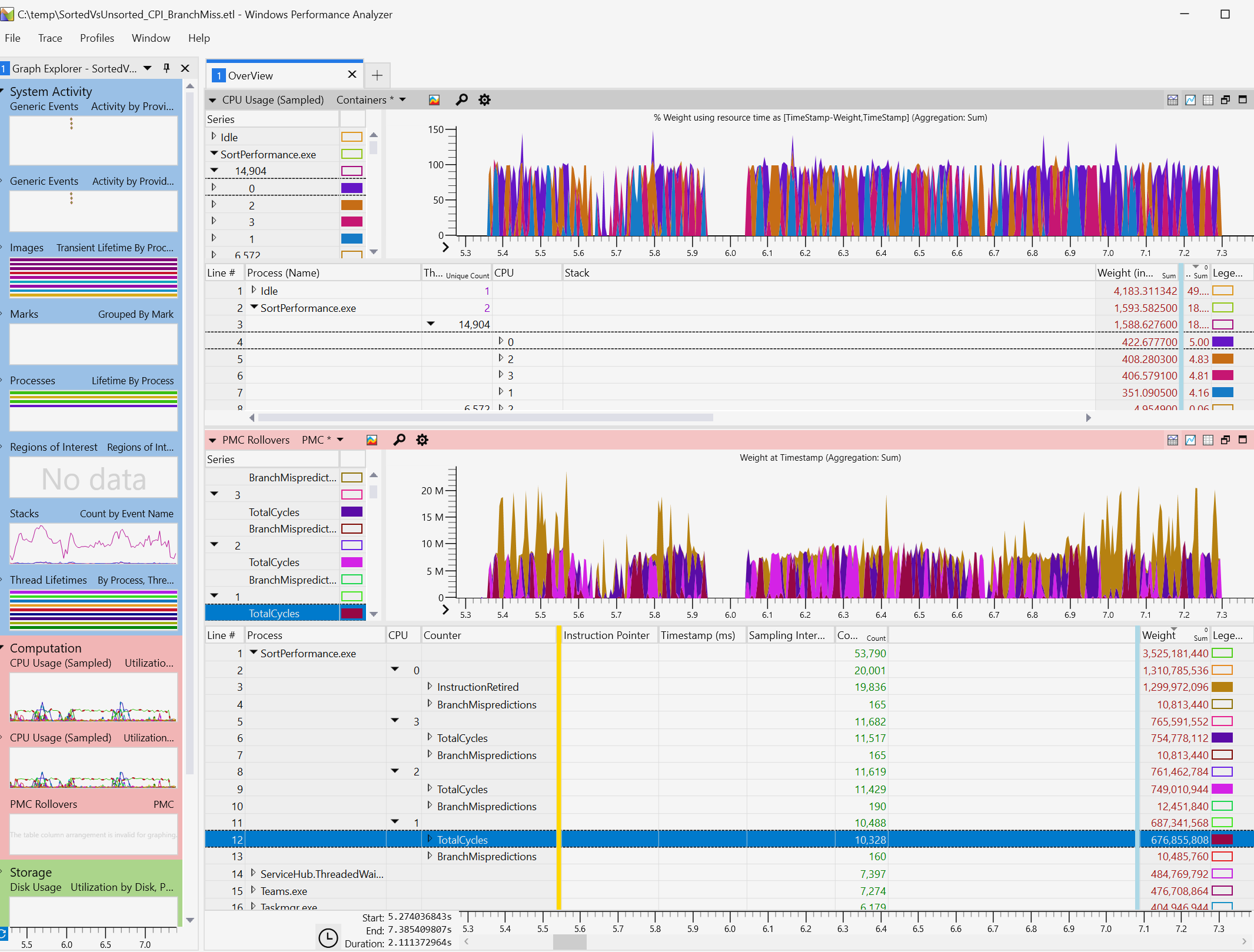

Since CPI makes only sense per Core I would expect the counter values to fire at per core level in a uniform way.

But for some reason the most busy core 0 has InstructionsRetired, but not a single TotalCycles event for that core. That makes no sense, at least in the way

WPA visualizes the data. xperf -i xxx.etl -a pmc shows similar garbage data

PmcInterrupt, 7562848, 3, SortPerformance.exe (1352), System.Private.CoreLib.dll!Unknown, TotalCycles, 0

PmcInterrupt, 7562880, 3, SortPerformance.exe (1352), System.Private.CoreLib.dll!Unknown, TotalCycles, 0

PmcInterrupt, 7562909, 3, SortPerformance.exe (1352), System.Private.CoreLib.dll!Unknown, TotalCycles, 0

PmcInterrupt, 7562937, 3, SortPerformance.exe (1352), System.Private.CoreLib.dll!Unknown, TotalCycles, 0

PmcInterrupt, 7562966, 3, SortPerformance.exe (1352), System.Private.CoreLib.dll!Unknown, TotalCycles, 0

This seems to be a longer journey. I had hoped that I could get something useful which can nicely be visualized with WPA.

At least my Counters profile is getting annotations

<SampledCounters>

<!-- Accordig to https://stackoverflow.com/questions/53840322/difference-between-llcmisses-and-cachemisses-on-hardware-counters the counters are first

defined in a generic way, which have then Processor Architecture specific latter synonyms.

wpr -pmcsources

Id Name Interval Min Max

0 Timer 10000 1221 1000000

2 TotalIssues == InstructionRetired 65536 4096 2147483647

6 BranchInstructions == BranchInstructionRetired 65536 4096 2147483647

10 CacheMisses == LLCMisses 65536 4096 2147483647

11 BranchMispredictions == BranchMispredictsRetired 65536 4096 2147483647

19 TotalCycles == UnhaltedCoreCycles 65536 4096 2147483647

*25 UnhaltedCoreCycles 65536 4096 2147483647

26 InstructionRetired 65536 4096 2147483647

27 UnhaltedReferenceCycles 65536 4096 2147483647

28 LLCReference 65536 4096 2147483647

*29 LLCMisses 65536 4096 2147483647

*30 BranchInstructionRetired 65536 4096 2147483647

*31 BranchMispredictsRetired 65536 4096 2147483647

32 LbrInserts (LastBranchRecord) 65536 4096 2147483647

33 InstructionsRetiredFixed 65536 4096 2147483647

34 UnhaltedCoreCyclesFixed 65536 4096 2147483647

35 UnhaltedReferenceCyclesFixed 65536 4096 2147483647

36 TimerFixed 10000 1221 1000000

-->

<SampledCounter Value="TotalCycles" Interval="65536"/>

<SampledCounter Value="InstructionRetired" Interval="65536"/>

<SampledCounter Value="BranchMispredictions" Interval="65536"/>

</SampledCounters>

I start to understand things a bit better. It would be perfect if we could arrange a chat. My Mail is

Alois DOT Kraus at Siemens-Healthineers.com

Replace DOT with .