Información general sobre los controladores de dispositivos periféricos de SPB

Un controlador de dispositivo periférico SPB controla un dispositivo periférico que está conectado a un bus periférico simple (SPB). Los registros de hardware de este dispositivo solo están disponibles a través del SPB. Para leer o escribir en el dispositivo, el controlador debe enviar solicitudes de E/S al controlador SPB. Solo este controlador puede iniciar transferencias de datos hacia y desde el dispositivo a través del SPB.

A partir de Windows 8, Windows proporciona compatibilidad con controladores para dispositivos periféricos en buses periféricos simples (SPB). Los SPB, como I2C y SPI, se usan ampliamente para conectarse a dispositivos de sensor de baja velocidad, como acelerómetros, dispositivos GPS y monitores de nivel de batería. En esta información general se describe cómo un controlador de dispositivos periféricos SPB, junto con otros componentes del sistema, controla un dispositivo periférico conectado a SPB.

Se puede crear un controlador de dispositivo periférico SPB para usar el marco de controladores en modo de usuario (UMDF) o el marco de controladores en modo kernel (KMDF). Para obtener más información sobre cómo desarrollar un controlador UMDF, consulte Introducción a UMDF. Para obtener más información sobre cómo desarrollar un controlador KMDF, consulte Introducción al marco de controladores en modo kernel.

Información de configuración del dispositivo

Los registros de hardware de un dispositivo periférico conectado a SPB no están asignados a la memoria. Solo se puede acceder al dispositivo a través del controlador SPB, que transfiere datos en serie hacia y desde el dispositivo a través del SPB. Para realizar operaciones de E/S, el controlador de dispositivo periférico SPB envía solicitudes de E/S al dispositivo y el controlador SPB realiza las transferencias de datos necesarias para completar estas solicitudes. Para obtener más información sobre las solicitudes de E/S que se pueden enviar a dispositivos periféricos en SPB, consulte Uso de la interfaz de solicitud de E/S de SPB.

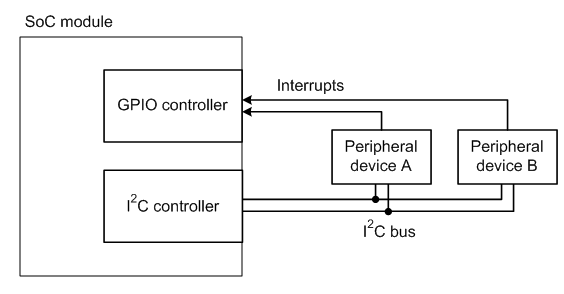

En el diagrama siguiente se muestra una configuración de hardware de ejemplo en la que un SPB (en este caso, un bus I2C) conecta dos dispositivos periféricos a un módulo de sistema en un chip (SoC). Los dispositivos periféricos son externos al módulo SoC y se conectan a cuatro pines del módulo. El módulo SoC contiene el procesador principal (no se muestra), además de un controlador I2C y un controlador de E/S de uso general (GPIO). El procesador usa el controlador I2C para transmitir datos en serie hacia y desde los dos dispositivos periféricos. Las líneas de solicitud de interrupción de estos dispositivos están conectadas a dos pines GPIO configurados como entradas de interrupción. Cuando un dispositivo señala una solicitud de interrupción, el controlador GPIO retransmite la interrupción al procesador.

Dado que el controlador GPIO y el controlador I2C de este ejemplo se integran en el módulo SoC, los registros de hardware están asignados a la memoria y el procesador puede acceder directamente a ellos. Sin embargo, el procesador puede acceder a los registros de hardware de los dos dispositivos periféricos solo indirectamente, a través del controlador I2C.

Un SPB no es un bus Plug and Play (PnP) y, por lo tanto, no se puede usar para detectar y configurar automáticamente nuevos dispositivos conectados al bus. Las conexiones de bus e interrupción de un dispositivo conectado a SPB suelen ser permanentes. Incluso si el dispositivo se puede desconectar de una ranura, esta ranura se suele dedicar al dispositivo. Además, un SPB no proporciona una ruta de acceso de hardware en banda para retransmitir solicitudes de interrupción desde un dispositivo periférico en el bus al controlador de bus. En su lugar, la ruta de acceso de hardware para las interrupciones es independiente del controlador de bus.

El proveedor de la plataforma de hardware almacena la información de configuración de un dispositivo periférico conectado a SPB en el firmware ACPI de la plataforma. Durante el inicio del sistema, el controlador ACPI enumera los dispositivos del bus para el administrador de PnP. Para cada dispositivo enumerado, ACPI proporciona información sobre el bus del dispositivo y las conexiones de interrupción. El administrador de PnP almacena esta información en un almacén de datos denominado centro de recursos.

Cuando se inicia el dispositivo, el administrador de PnP proporciona al controlador del dispositivo un conjunto de recursos de hardware que encapsulan la información de configuración que almacena el centro de recursos para el dispositivo. Estos recursos incluyen un identificador de conexión y un número de interrupción. El identificador de conexión encapsula la información de conexión de bus, como el controlador SPB, la dirección del bus y la frecuencia del reloj del bus. Para poder enviar solicitudes de E/S al dispositivo, el controlador debe usar primero el identificador de conexión para abrir una conexión lógica al dispositivo. El número de interrupción es un recurso de interrupción de Windows al que el controlador puede conectar su rutina de servicio de interrupción (ISR). El controlador se puede migrar fácilmente de una plataforma de hardware a otra porque el identificador de conexión y el número de interrupción son abstracciones de alto nivel que ocultan información específica de la plataforma sobre el bus físico y las conexiones de interrupción.

Capas de software y hardware

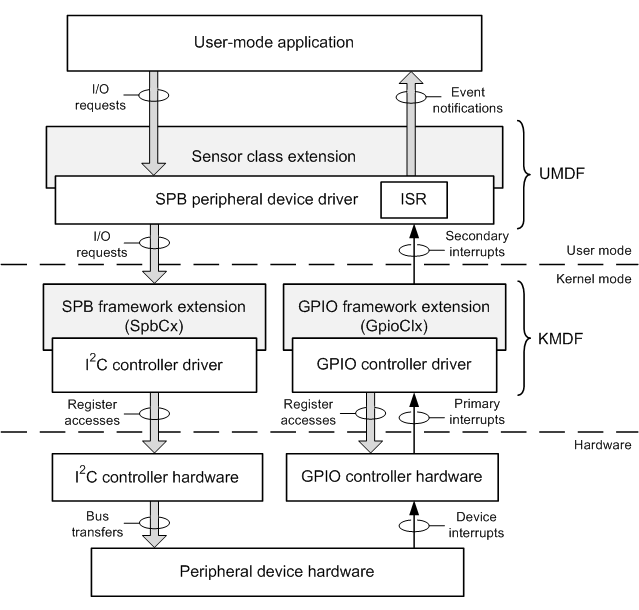

En el diagrama de bloques siguiente se muestran las capas de software y hardware que conectan un dispositivo periférico de un SPB a un programa de aplicación que usa el dispositivo. El controlador de dispositivo periférico SPB de este ejemplo es un controlador UMDF. El dispositivo periférico (en la parte inferior del diagrama) es un dispositivo sensor (por ejemplo, un acelerómetro). Como en el diagrama anterior, el dispositivo periférico está conectado a un bus I2C y señala solicitudes de interrupción a través de un pin en un controlador GPIO.

Los tres bloques que se muestran en gris son módulos proporcionados por el sistema. A partir de Windows 7, la extensión de clase de sensor está disponible como una extensión específica del sensor para UMDF. A partir de Windows 8, la extensión de marco de SPB (SpbCx) y la extensión de marco GPIO (GpioClx) están disponibles como extensiones para KMDF que realizan funciones específicas de controladores SPB y controladores GPIO, respectivamente.

En la parte superior del diagrama anterior, la aplicación llama a los métodos de la API de sensor o API de ubicación para comunicarse con el dispositivo del sensor. A través de estas llamadas, la aplicación puede enviar solicitudes de E/S al dispositivo y recibir notificaciones de eventos del dispositivo. Para obtener más información sobre estas API, consulte Introducción a la plataforma de sensores y ubicaciones en Windows.

Cuando la aplicación llama a un método que requiere comunicación con el controlador de dispositivo periférico SPB, la API del sensor o la API de ubicación crea una solicitud de E/S y la envía al controlador de dispositivo periférico SPB. El módulo de extensión de clase sensor ayuda al controlador a controlar estas solicitudes de E/S. Cuando el controlador recibe una nueva solicitud de E/S, el controlador entrega inmediatamente la solicitud a la extensión de clase de sensor, que pone en cola la solicitud hasta que el controlador esté listo para controlarla. Si una solicitud de E/S de la aplicación requiere la transferencia de datos hacia o desde el dispositivo periférico, el controlador del dispositivo periférico SPB crea una solicitud de E/S para esta transferencia y envía la solicitud al controlador I2C. SpbCx y el controlador I2C controlan conjuntamente estas solicitudes.

SpbCx es un componente proporcionado por el sistema que administra las colas de solicitudes de E/S para un controlador SPB, como el controlador I2C de este ejemplo. El controlador I2C, proporcionado por el proveedor de hardware para el controlador, administra todas las operaciones específicas del hardware en el controlador I2C. Por ejemplo, el controlador accede a los registros de hardware asignados a memoria del controlador para iniciar transferencias de datos hacia y desde el dispositivo periférico a través del bus I2C.

El dispositivo periférico indica una solicitud de interrupción cuando se produce un evento de hardware que requiere atención del controlador de dispositivo periférico SPB o de la aplicación en modo de usuario. La línea de interrupción del dispositivo periférico está conectada a un pin GPIO configurado para recibir solicitudes de interrupción. Cuando el dispositivo señala una interrupción al pin GPIO, el controlador GPIO señala una interrupción al procesador. En respuesta a esta interrupción, el controlador de captura de interrupciones del kernel llama a la ISR de GpioClx. Esta ISR consulta el controlador GPIO que, a continuación, accede a los registros de hardware asignados a memoria del controlador GPIO para identificar el pin GPIO de interrupción. Para silenciar la interrupción, el controlador GPIO borra (si la interrupción está desencadenada por el borde) o enmascara (si está desencadenada por nivel) la solicitud de interrupción en el pin GPIO. La interrupción debe silenciarse para evitar que el procesador vuelva a tomar la misma interrupción cuando el controlador de captura vuelva. Para una interrupción desencadenada por nivel, la ISR del controlador de dispositivo periférico SPB debe acceder a los registros de hardware del dispositivo periférico para borrar la interrupción antes de que se pueda desenmascarar el pin GPIO.

Antes de que vuelva el controlador de captura de interrupción del kernel, programa la ISR en el controlador de dispositivo periférico SPB para que se ejecute en IRQL = PASSIVE_LEVEL. A partir de Windows 8, un controlador UMDF puede conectar su ISR a una interrupción que el controlador recibe como un recurso abstracto de interrupción de Windows; para obtener más información, consulte Control de interrupciones. Para determinar a qué ISR llamar, el sistema operativo busca la interrupción virtual que se asigna al pin GPIO de interrupción y busca la ISR que está conectada a la interrupción. Esta interrupción virtual se etiqueta como una interrupción secundaria en el diagrama anterior. En cambio, la interrupción de hardware del controlador GPIO se etiqueta como una interrupción principal.

Dado que la ISR del controlador de dispositivo periférico SPB se ejecuta en el nivel pasivo, la ISR puede usar solicitudes de E/S sincrónicas para acceder a los registros de hardware en el dispositivo periférico. La ISR puede bloquearse hasta que se completen estas solicitudes. La ISR, que se ejecuta con una prioridad relativamente alta, debe volver lo antes posible y aplazar todo el procesamiento en segundo plano de una interrupción a una rutina de trabajo que se ejecute con una prioridad menor.

En respuesta a la interrupción secundaria, el controlador del dispositivo periférico SPB publica un evento en la extensión de clase de sensor, que notifica a la aplicación en modo de usuario del evento a través de la API del sensor o la API de ubicación.