Painel de Estado

O painel Estado exibe expressões boolianas para os valores das variáveis no driver, no modelo do sistema operacional e na regra. O SDV usa essas expressões para construir uma abstração do driver, do modelo do sistema operacional e da regra e as usa na verificação.

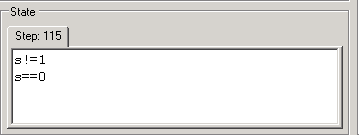

A captura de tela a seguir mostra um exemplo de painel Estado no Visualizador de Defeitos.

O painel Estado é um componente do Visualizador de Defeitos. Quando um elemento de código é realçado no painel Árvore de Rastreamento e a linha correspondente do código-fonte é realçada no painel Código-Fonte, o painel Estado exibe as expressões boolianas (do conjunto de expressões que o SDV está rastreando para o driver) que são avaliadas como TRUE antes que a linha de código seja executada.

Acompanhamento de expressões boolianas

Ao verificar cada regra para o driver, o SDV rastreia um conjunto de expressões boolianas. As expressões boolianas exibidas no painel Estado são as expressões nesse conjunto que são avaliadas como TRUE. Se o elemento no painel Árvore de Rastreamento alterar o valor de qualquer expressão, o conteúdo do painel Estado será alterado para exibir o novo conjunto de expressões que são avaliadas como TRUE.

Interpretando expressões no painel de estado

A maioria das expressões que aparecem no painel Estado estão relacionadas a variáveis evidentes no código de regra. Você pode usar o código-fonte para a regra (no arquivo RuleName.slic no painel Código-Fonte ) para ajudá-lo a interpretar as expressões.

No entanto, algumas expressões aparecem no painel Estado sem detalhes sobre sua representação interna que podem ajudá-lo a interpretá-las. Por exemplo,

x!=x

Para SDV, essa expressão representa uma condição na qual o valor da variável x neste ponto no rastreamento não é igual ao valor da mesma variável em um ponto diferente no rastreamento. Use o código-fonte do driver, o código-regra (*.slic) e os elementos no painel Árvore de Rastreamento para ajudá-lo a interpretar as expressões.

Guias de Etapa no Painel de Estado

As expressões boolianas no painel Estado são exibidas em guias. Cada guia representa uma etapa no rastreamento por meio de todo o código-fonte usado na verificação. O número na guia etapa representa a ordem dessa etapa no rastreamento.

Normalmente, como cada linha do código-fonte representa apenas uma etapa no rastreamento, haverá apenas uma guia de etapa no painel Estado . No entanto, o código complexo pode gerar muitas etapas.

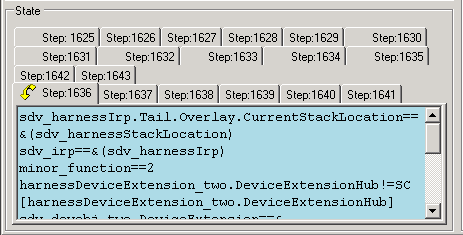

Por exemplo, a captura de tela a seguir mostra o painel Estado exibindo uma linha de código que inclui um ponteiro de função. Nesse caso, cada guia de etapa representa uma etapa na resolução do ponteiro, a chamada da função apontada e seu resultado. (O número de guias de etapas revela quantas etapas são necessárias para que o SDV resolve o ponteiro da função.)

Para exibir cada guia de etapa no painel Estado na ordem, selecione a linha de código associada no painel Código-Fonte . Em seguida, clique na linha de código no painel Código-Fonte repetidamente. Sempre que você clica na linha de código selecionada, o SDV exibe a próxima guia da etapa até que você tenha percrado todas as guias da etapa. A seta amarela curva indica a etapa selecionada.

Você também pode clicar em qualquer guia no painel Estado para exibir seu conteúdo.

Comentário

O SDV geralmente rastreia expressões no painel Estado que não aparecem na regra e não parecem estar diretamente relacionadas à regra. Essas expressões resultam de heurística sofisticada que o SDV usa em suas tentativas de correlacionar valores diferentes e diferentes violações de regra. Em algumas situações, o SDV não pode avaliar corretamente a expressão. Nesses casos, o SDV fornece uma mensagem informando que o estado atual é desconhecido e exibe a expressão da etapa com o último estado conhecido. Confira o exemplo de código a seguir para obter uma explicação:

Unknown state. Last known state from step 120.

sdv irql current ==2

sdv irql current!=1

sdv irql current!=0